Cabecera-Aula

Eduki publikatzailea

Txip Gela

Chip SoC4sensing Katedrak mikroelektronika ikasleei, enpresei eta, oro har, gizarteari zabaltzeko jarduerak bultzatzen ditu. Jarduera horien helburu nagusia da sektorean beharrezkoak diren profesionalak diren titulazioetara talentua erakartzea. Horretarako, diseinu elektronikoaren eta mikroelektronikoaren arloan jarduera profesional bat garatzeak ematen dituen aukerak erakutsi nahi zaizkio gizarteari.

Hedapen-helburuak betetzeko inpaktu-tresna bat SoC4sensing-etik abiarazitako Txip Gela da. Gela honek Bilboko Ingeniaritza Eskolako Enpresa Gela formatua du.

Enpresa Gelak Eskolan bertan kokatutako guneak dira, eta ikasgelak babesten dituzten erakundeetan ikasleen interesa sustatzeko eta sustatzaileentzat interesgarriak diren I+G+b jarduerak sustatzeko sortu dira. Lankidetza-tresna eraginkorra dira Bilboko Ingeniaritza Eskolaren eta enpresen artean, beren sailen bitartez, bai ikerketarekin, garapen teknologikoarekin eta berrikuntzarekin lotutako jardueretan, bai prestakuntzari dagokion guztian, dela etorkizuneko ingeniariena, dela birziklatzearekin eta enpresetako langileen etengabeko prestakuntzarekin lotutako jardueretan. Gaur egun, 12 enpresa-gela daude.

Beraz, Chip Gelak katedran egindako jarduerak ikasleei, enpresei eta, oro har, gizarteari ikusaraztea bultzatzen du.

Eduki publikatzailea

RISC-V based Spacewire Node implemented on European Radiation Hardened FPGA Devices

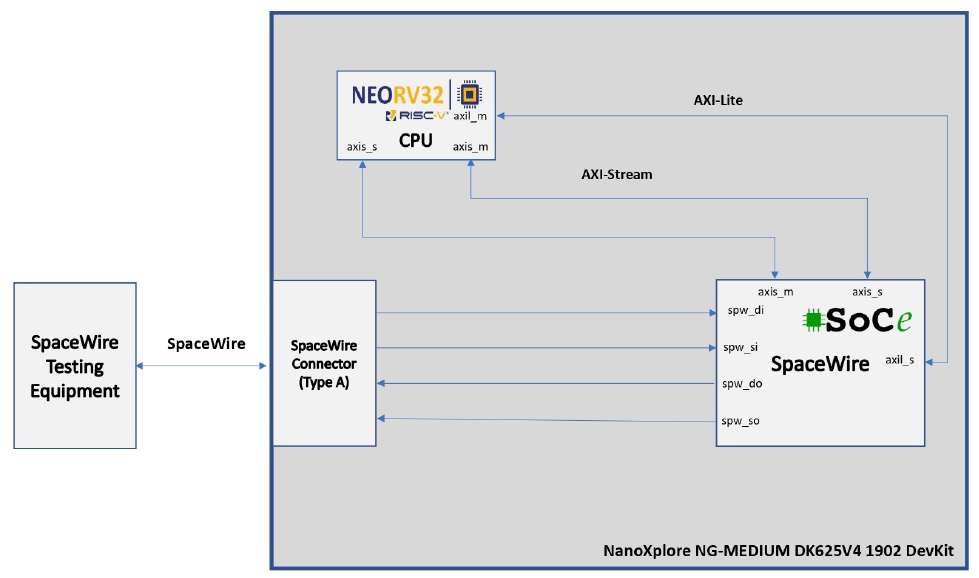

This research presents a SoC implementation of a SpaceWire node, consisting of an open 32-bit RISC-V CPU and an HDL SpaceWire IP core on a European Radiation-Hardened SRAM FPGA (NanoXplore) and a Microchip (Microsemi) FLASH-based FPGA.

Lehenengo argitaratze data: 2026/01/22

SpaceWire is a communication protocol widely adopted in spacecraft for connecting instruments to data processors, mass memory and control processors. Field-Programmable Gate Arrays (FPGAs) are a popular choice for implementing SpaceWire nodes due to their flexibility in meeting the unique requirements of each program or product.

Section II introduces the SpaceWire protocol and the two FPGA technologies used for the implementations.

Section III presents the high-level block diagram of a generic SpaceWire node.

Section IV provides details of the two implementations developed, with the first using a 32-bit RISC-V CPU on a NanoXplore

SRAM-based FPGA, and the second using a 32-bit RISC-V CPU on a Microchip (Microsemi) FLASH-based FPGA.

Section V compares the obtained results in terms of FPGA resources and power consumption.

Esteka

Irudi galeria

Eduki publikatzailea