Cabecera-Investigación

Eduki publikatzailea

Ikerkuntza

Sistema kritikoetarako soluzio mikroelektronikoen ikerketa Chip SoC4sensing Katedraren zutabe bat da. Hauek dira ikerketa-planaren helburuak:

- Produktu mikroelektronikoetarako soluzioen diseinuan aurrera egitea ahalbidetuko duten ikerketa-ildoak bultzatzea, bereziki epe labur eta ertainean aprobetxa daitezkeen gailu erdieroaleak.

- Prestakuntza Planean aplikagarriak izango diren zeharkako kontzeptuak eta gaitasunak aztertzea eta garatzea.

Zehazki, katedran sustatutako jarduketek honako gai hauek dituzte ardatz:

- System-on-Chip (SoC) sistemarako sartutako PUZen arkitekturak:

Proposatutako jardueren bidez, RISC-V eta ARM mikroprozesadoreetan oinarritutako SoC azpisistemen ikerketa eta garapen esperimentala jorratzen dira. Neurrira garatutako koprozesadoreak integratuz RISC-V arkitektura egokitzeko aukera.

- Belaunaldi berriko industria-komunikazioko sistemetarako arkitektura mikroelektronikoak:

Lan-ildo honetan bultzatutako jarduerek OT (denbora errealeko) eta IT komunikazioak osatzen dituzten sistema kritikoetarako komunikazio-sistema berriak inplementatzeko hardware soluzioak ikertu eta garatzen dituzte. Industria-sektoreak (4.0 industria), ENERGIA (Smart Grid) eta Aeroespaziala dira ekarpen horien onuradun nagusiak.

- Arkitektura mikroelektronikoak Sentsore aurreratua duten sistemetan konputazio-aplikazioetarako:

Ikerketa-lerro honek berariazko aplikazio sentsoriko batean (Ikusmen Sentsore Dinamikoak) espezializatutako ikerketa- eta garapen-jarduerak jorratzen ditu, garatutako SoC azpisistemetan integratu daitekeen Chiplet garapen esperimental batean gainbehera egitea ahalbidetuko duena. Arlo honetako ekarpenak zuzenean aplikatzen dira industrian, automobilgintzan eta aeroespazioan.

Eduki publikatzailea

RISC-V based Spacewire Node implemented on European Radiation Hardened FPGA Devices

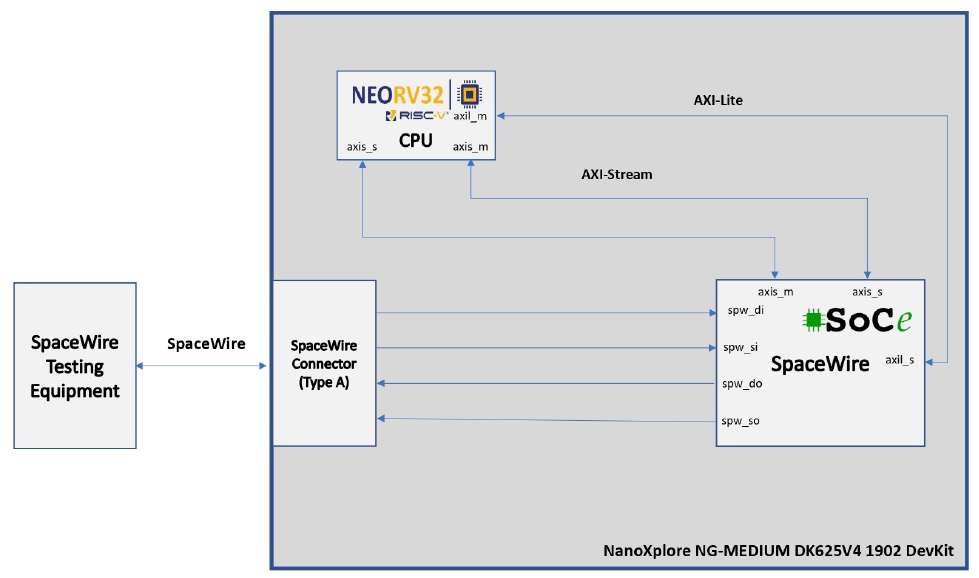

This research presents a SoC implementation of a SpaceWire node, consisting of an open 32-bit RISC-V CPU and an HDL SpaceWire IP core on a European Radiation-Hardened SRAM FPGA (NanoXplore) and a Microchip (Microsemi) FLASH-based FPGA.

Lehenengo argitaratze data: 2026/01/22

SpaceWire is a communication protocol widely adopted in spacecraft for connecting instruments to data processors, mass memory and control processors. Field-Programmable Gate Arrays (FPGAs) are a popular choice for implementing SpaceWire nodes due to their flexibility in meeting the unique requirements of each program or product.

Section II introduces the SpaceWire protocol and the two FPGA technologies used for the implementations.

Section III presents the high-level block diagram of a generic SpaceWire node.

Section IV provides details of the two implementations developed, with the first using a 32-bit RISC-V CPU on a NanoXplore

SRAM-based FPGA, and the second using a 32-bit RISC-V CPU on a Microchip (Microsemi) FLASH-based FPGA.

Section V compares the obtained results in terms of FPGA resources and power consumption.

Esteka

Irudi galeria

Eduki publikatzailea