Cabecera-Aula

Publicador de contenidos

Aula Chip

La Cátedra Chip SoC4sensing impulsa actividades de difusión de la microelectrónica a los Estudiantes, Empresas y a la Sociedad en general. El objetivo principal de estas actuaciones es atraer talento a las titulaciones que egresan profesionales necesarios en el sector. Para ello, se busca visualizar a la sociedad las posibilidades que brinda el desarrollo de una actividad profesional en el campo del diseño electrónico y microelectrónico.

Una herramienta de impacto para cumplir los objetivos de difusión es el Aula Chip lanzada desde SoC4sensing. Esta Aula tiene el formato de Aula de Empresa de la Escuela de Ingeniería de Bilbao.

Las Aulas de Empresa son espacios situados en la propia Escuela y están creadas para incentivar el interés del alumnado en las entidades que patrocinan las aulas y para promover las actividades de I+D+i de interés para los promotores. Son un instrumento eficaz de colaboración entre la Escuela de Ingeniería de Bilbao, a través de sus departamentos, y las empresas, tanto en actividades relacionadas con la investigación, el desarrollo tecnológico y la innovación, como en todo lo referente a la formación, sea de los futuros ingenieras/os, sea en actividades relacionadas con el reciclaje y la formación continua de personal de las empresas. Actualmente hay 12 Aulas de Empresa.

Por tanto, el Aula Chip impulsa la visibilidad de las actuaciones realizadas en la Cátedra al alumnado, empresas y a la sociedad en general.

Publicador de contenidos

Nodo Spacewire basado en RISC-V implementado en dispositivos FPGA europeos reforzados contra la radiación

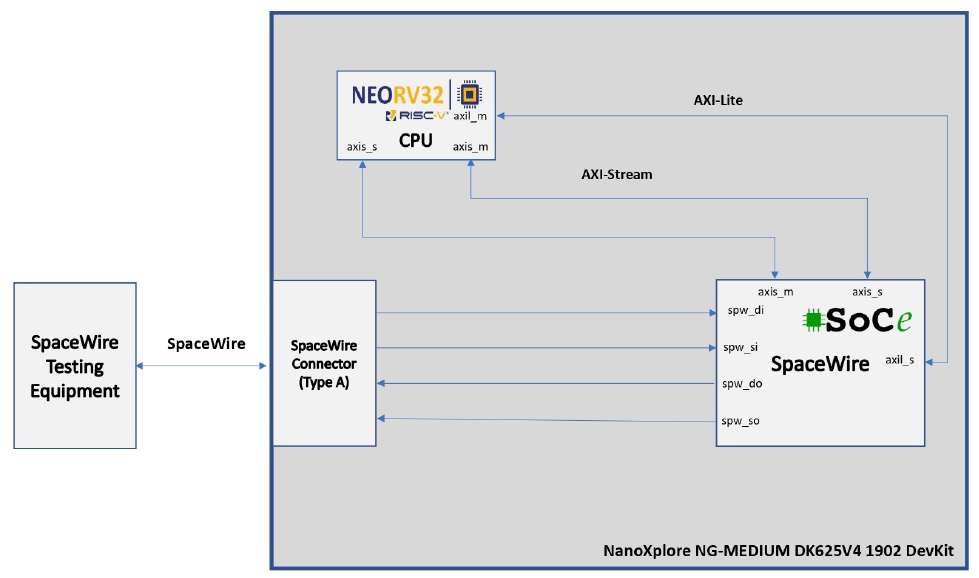

Esta investigación presenta una implementación SoC de un nodo SpaceWire, que consta de una CPU RISC-V de 32 bits abierta y un núcleo IP SpaceWire HDL en una FPGA SRAM resistente a la radiación europea (NanoXplore) y una FPGA basada en FLASH de Microchip (Microsemi).

Fecha de primera publicación: 22/01/2026

SpaceWire es un protocolo de comunicación ampliamente adoptado en las naves espaciales para conectar instrumentos a procesadores de datos, memorias masivas y procesadores de control. Las matrices de puertas programables en campo (FPGA) son una opción muy popular para implementar nodos SpaceWire debido a su flexibilidad para satisfacer los requisitos únicos de cada programa o producto.

La Sección II presenta el protocolo SpaceWire y las dos tecnologías FPGA utilizadas en las implementaciones.

La Sección III presenta el diagrama de bloques de alto nivel de un nodo SpaceWire genérico.

La Sección IV detalla las dos implementaciones desarrolladas: la primera utiliza una CPU RISC-V de 32 bits en una FPGA basada en SRAM NanoXplore, y la segunda utiliza una CPU RISC-V de 32 bits en una FPGA basada en FLASH de Microchip (Microsemi).

La Sección V compara los resultados obtenidos en términos de recursos de la FPGA y consumo de energía.

Galería de imágenes

Publicador de contenidos