Cabecera-Investigación

Publicador de contenidos

Investigación

La investigación en soluciones microelectrónicas para sistemas críticos es un pilar de la Cátedra Chip SoC4sensing. Los objetivos del plan de investigación son:

- Impulsar líneas de investigación que permitan avanzar en el diseño de soluciones para productos microelectrónicos, específicamente dispositivos semiconductores que puedan ser aprovechados a corto y medio plazo.

- Explorar y desarrollar conceptos y capacidades transversales que serán aplicables en el Plan de Formación.

En concreto las actuaciones en actuación promovidas en la cátedra están focalizadas en las siguientes temáticas:

- Prototipado de un dispositivo semiconductor SoC con comunicaciones Ethernet de alta disponibilidad y CPU RISC-V en lógica reconfigurable de tecnología SRAM Intel-Altera de nueva generación

El obejtivo de este proyecto es obtener un diseño SoC basado en CPU RISC-V de un nodo de comunicaciones Ethernet de alta disponibilidad (HSR/PRP) implementado sobre la Tecnología tecnología SRAM Intel-Altera de nueva generación

- Diseño de Circuitos Integrados Digitales con FOSS (Free and Open Source Software) EDA

Mediante la presente convocatoria, la Cátedra Chip Universidad-Empresa SoC4sensing el curso de extensión universitaria denominado Diseño de Circuitos Integrados Digitales con FOSS EDA de impartición en la Escuela de Ingeniería de Bilbao. En este curso podrás adquirir las competencias básicas en el diseño de circuitos integrados digitales mediante el uso de estas herramientas y sentar así las bases para tu futuro profesional en el emergente campo de la microelectrónica.

- Sincronización y control de sistemas de sensores cuánticos remotos controlados con dispositivos semiconductores RFSoC

El objetivo principal de este trabajo es diseñar una red de sistemas de control de instrumentos de control de sistemas cuánticos distribuidos mediante una red determinística TSN. Los sistemas de instrumentación estará basados en los dispotiviso semiconductores de tipo RFSoC que integran en el mismo circuito integrado todos los elementos de valor añadido especificios de la aplicación: el hardware digital de comunicaciones, el hardware de procesamiento digital de señal, el RF y el software de aplicacion.

- Arquitecturas de CPUs embebidas para System-on-Chip (SoC):

Mediante las actuaciones propuestas se abordan la investigación y el desarrollo experimental de sub-sistemas SoC basados en microprocesadores RISC-V y ARM. La posibilidad de adaptar la arquitectura RISC-V integrando coprocesadores desarrollados a medida para

- Arquitecturas microelectrónicas para sistemas de comunicación industriales de nueva generación:

Las actividades impulsadas en esta línea de trabajo abordan la investigación y el desarrollo de soluciones hardware para implementar los nuevos sistemas de comunicación para sistemas críticos que integran las comunicaciones OT (de tiempo real) e IT. Los sectores industriales (Industria 4.0), ENERGÍA (Smart Grid) y Aeroespacial son los principales beneficiarios de estas contribuciones.

- Arquitecturas microelectrónicas para aplicaciones de computación en sistemas con Sensórica avanzada:

Esta línea de investigación aborda actividades de investigación y desarrollo altamente especializadas en una aplicación sensórica especifica, Sensores de Visión Dinámicos, que permitirá declinar en un desarrollo Chiplet experimental integrable en los subsistemas SoC desarrollados. Las contribuciones en esta área son de aplicación directa en la Industria, Automoción y Aeroespacio.

Publicador de contenidos

Nodo Spacewire basado en RISC-V implementado en dispositivos FPGA europeos resistentes a la radiación

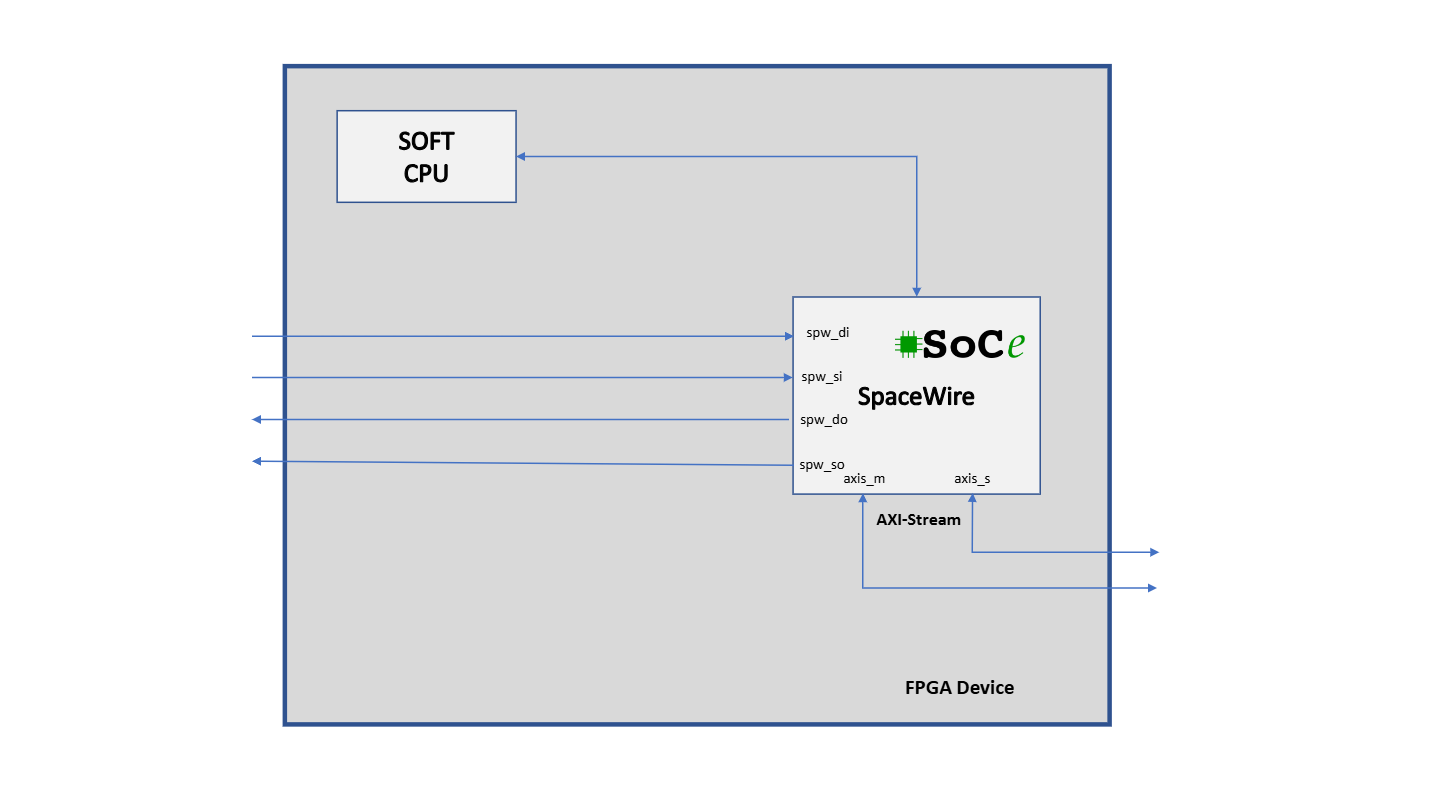

Esta investigación presenta una implementación SoC de un nodo SpaceWire, consistente en una CPU RISC-V abierta de 32 bits y un núcleo IP HDL SpaceWire en una FPGA europea SRAM endurecida contra la radiación (NanoXplore) y una FPGA basada en FLASH de Microchip (Microsemi).

Fecha de primera publicación: 21/01/2025

Esta investigación presenta una implementación SoC de un nodo SpaceWire, consistente en una CPU RISC-V abierta de 32 bits y un núcleo IP HDL SpaceWire en una FPGA europea SRAM endurecida contra la radiación (NanoXplore) y una FPGA basada en FLASH de Microchip (Microsemi). Ambos diseños se implementaron y simularon utilizando las suites de diseño comerciales proporcionadas por cada proveedor. La verificación de los diseños se llevó a cabo utilizando dos kits de evaluación, mientras que la validación de los nodos SoC se realizó mediante pruebas de conformidad utilizando equipos de pruebas comerciales de SpaceWire.

Publicador de contenidos