Cabecera-Noticias

Publicador de contenidos

Nodo Spacewire basado en RISC-V implementado en dispositivos FPGA europeos resistentes a la radiación

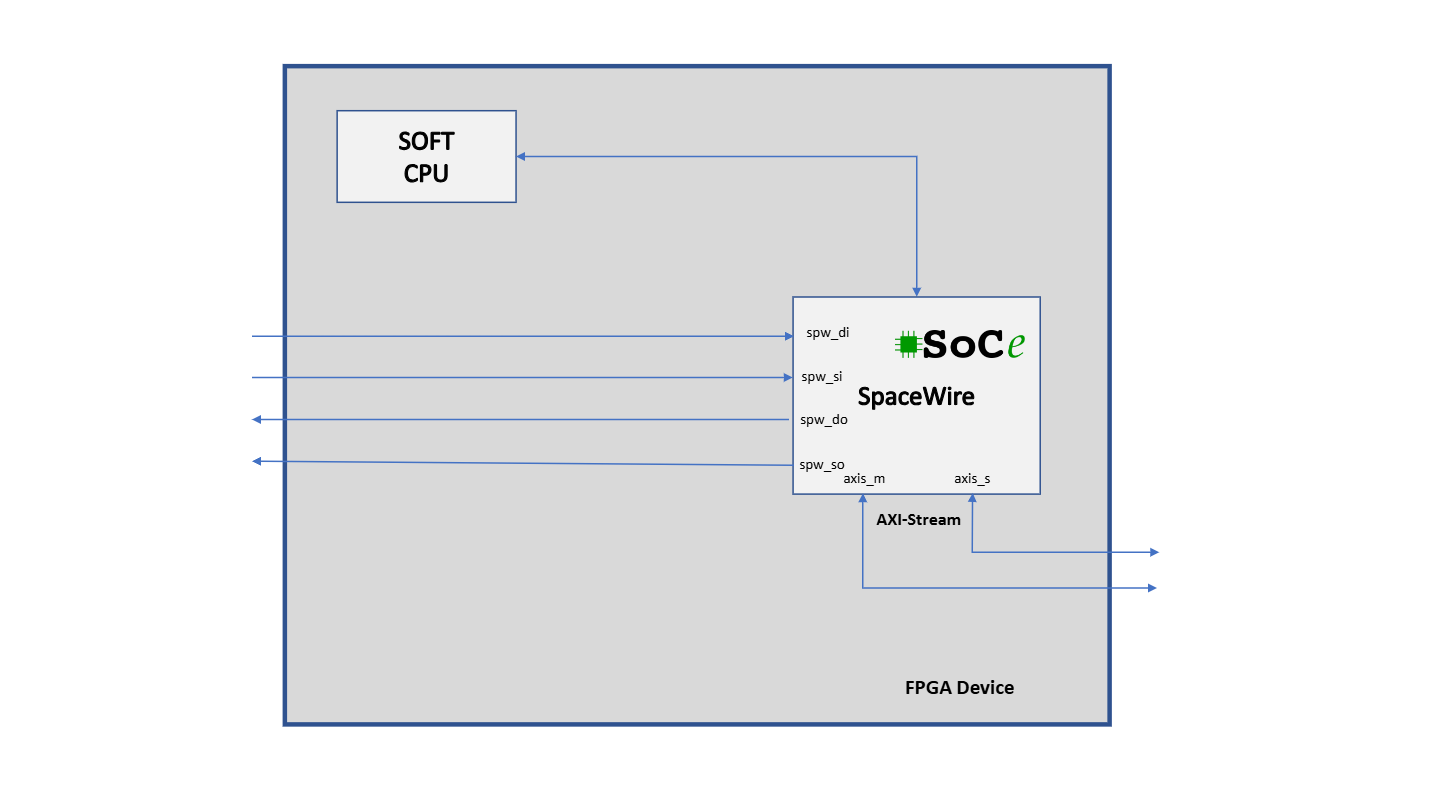

Esta investigación presenta una implementación SoC de un nodo SpaceWire, consistente en una CPU RISC-V abierta de 32 bits y un núcleo IP HDL SpaceWire en una FPGA europea SRAM endurecida contra la radiación (NanoXplore) y una FPGA basada en FLASH de Microchip (Microsemi).

Fecha de primera publicación: 21/01/2025

Esta investigación presenta una implementación SoC de un nodo SpaceWire, consistente en una CPU RISC-V abierta de 32 bits y un núcleo IP HDL SpaceWire en una FPGA europea SRAM endurecida contra la radiación (NanoXplore) y una FPGA basada en FLASH de Microchip (Microsemi). Ambos diseños se implementaron y simularon utilizando las suites de diseño comerciales proporcionadas por cada proveedor. La verificación de los diseños se llevó a cabo utilizando dos kits de evaluación, mientras que la validación de los nodos SoC se realizó mediante pruebas de conformidad utilizando equipos de pruebas comerciales de SpaceWire.